## **Arnold Wiemers**

# Hochschulseminar und Tutorial Leiterplatten 72

...Konstruktion und Analyse von CAD-Layouts und Leiterplatten

Allgemeine und spezielle Regeln für die CAD-Konstruktion. Hintergründe und Vorgaben für die Fertigung von Leiterplatten als Basis hochleistungsfähiger Baugruppen. Datenlogistik und Analyse von Layoutspezifikationen.

## Wer wird mit dem Seminar/Tutorial "Leiterplatten 72 ...Konstruktion und Analyse von CAD-Layouts und Leiterplatten" angesprochen ?

Die Möglichkeiten der Leiterplattentechnologie bestimmen die Freiräume bei der Konstruktion von CAD-Layouts und die langfristige, zuverlässige Funktion von Baugruppen in Fahrzeugen, Anlagen und Maschinen. Die Leiterplattentechnologie steht im Zentrum, ist aber verknüpft mit der Konstruktion des CAD-Layoutes und der Produktion von Baugruppen. Durch die Einbindung der Baugruppentechnologie ergibt sich ein gesamtheitlicher Blick auf die Anforderungen an elektronische Baugruppen.

Die *Konstrukteure* elektronischer Schaltungen und die *CAD-Designer* und *CAD-Designerinnen* erkennen die Zusammenhänge zwischen der virtuellen CAD-Konstruktion und der Auswirkung auf die reale Produktion und Funktion von elektronischen Geräten. Die Teilnehmer lernen, vor dem Hintergrund gegebener Produktionstoleranzen die Vorgaben für die Routing-Constraints in der CAD-Bibliothek richtig zu hinterlegen.

"Leiterplatten 72 ...Konstruktion und Analyse von CAD-Layouts und Leiterplatten" erläutert anschaulich die Leiterplattentechnologie und ihren nachhaltigen Einfluß auf die Konzeptionierung einer Baugruppe. Sie lernen alle Fertigungsverfahren kennen, die für die Produktion elektronischer Baugruppen erforderlich sind. Die fachgerechte Analyse der Produktdokumentation und der Produktionsdaten erlaubt die verbindliche Einschätzung der Produzierbarkeit eines CAD-Designs. Sie erlangen eine interdisziplinäre Kompetenz, die sie in den Stand ver-

setzt, eigenständig über die Konstruktion wirtschaftlich effektiver und vorhersagbar zuverlässiger Elektronikprodukte entscheiden zu können.

Das Seminar ist auch für *CAM-Bearbeiter/innen* der LP-Hersteller von Bedeutung, weil es die Zusammenhänge zwischen CAD und Leiterplatte erläutert. Es fördert damit auch das partnerschaftliche Miteinander auf der Linie "CAD - CAM - Leiterplatte - Baugruppe".

Die übersichtliche Darstellung der Themen ist ebenso interessant für alle *Entscheidungsträger im Bereich Design und Leiterplatte*, deren Aufgabe es ist, das Produkt "Baugruppe" führend und beratend zu begleiten.

## Leiterplatten Akademie

## Baugruppen 1

Klassische und spezielle Lösungen für den Einsatz elektronischer Baugruppen in den unterschiedlichsten Anwendungsbereichen.

Baugruppen für den industriellen und den kommerziellen Einsatz. Beachtung der Betriebsumgebung.

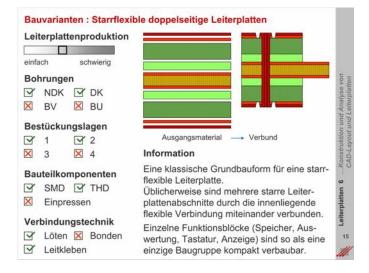

#### Starre + flexible Baugruppe

"Starre" und "flexible" Leiterplatten stehen nicht solitär für die gesamte Anwendung. Durch die Kombination eigenständiger Baugruppen zu einem Gesamtsystem entstehen sehr kompakte und sehr leistungsfähige elektronische Geräte. Auf kleinstem Raum sind damit Produkte machbar, die mit konventioneller Verdrahtung über Kabel und Stecker nicht umsetzbar gewesen wären. Die starrflexiblen Baugruppen sind deshalb eine Schlüsseltechnologie für die Konstruktion hochwertiger Wirtschaftsgüter.

Flexibler Bereich für die Verbindung der diversen mechanischen Komponenten. Die Motoren für die Blenden, die Fokussierung und die Sensorik müssen in Kommunikation gebracht werden.

Starrer Bereich als Träger der Elektronik für die Auswertung der Sensorik bzw der optischen Systeme.

## Baugruppen 2

Anwendungen von starren, flexiblen und starrflexiblen Leiterplatten bzw. Baugruppen für diverse Gerätekonzepte.

Flexible Leiterplatten als diskrete Übertragungsleitungen und als Quasi-Verbindungskabel für die Geräteverkabelung.

#### Montage : SMD

SMD-Bauteile sind leicht und klein und benötigen keine Bohrung, die den Platz für das Routen von Leiterbahnen auf den Innenlagen einschränken würde.

#### Beispiel (SMD-THT-Baugruppe ds)

Vornehmliche SMD-Bestückung von — Widerständen, Kondensatoren, Dioden und ICs. Die schwereren Elektrolytkondensatoren und Relais sind bedrahtet. Die Bestückung erfolgt nur auf dem Toplayer.

#### Beispiel (SMD-THT-Baugruppe es)

SMD-Bestückung auf dem Toplayer. Diverse bedrahtete Kondensatoren sind vom Bottomlayer aus bestückt. Das Material ist einseitiges FR2. Die NDK-Bohrungen und die Kontur sind gestanzt.

## Klassifizierung von Baugruppen

Eine Übersicht zu den Strategien für die Montage elektronischer Komponenten auf einer Leiterplatte.

Löten, Bonden und Einpressen als prinzipielle Verfahren.

Wechselwirkungen zwischen den Basismaterialien, den Lagenaufbauten und der Montagetechnik.

#### **Bauformen**

THD und SMD-Komponenten.

Gehäuseformen und Abmaße für elektronische und mechanische Bauteile. Standardisierte Grundflächen und Platzbedarf für das Routing. Auswirkung der Misch- und doppelseitigen Bestückung auf die langfristige Qualität der Leiterplatte.

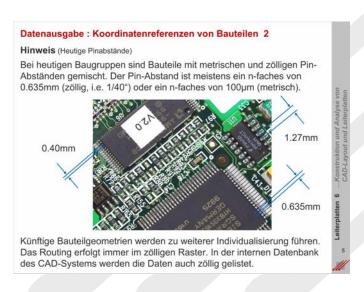

#### Grundraster

Standardraster für Bauteile auf der Basis metrischer und/oder zöllige Koordinaten.

Klassische Rastermaße für die Verdrahtung von THDs und SMDs in elektronischen Schaltungen.

## Lagenaufbau + Montage

Allgemeine Strategien für den Aufbau von starren, flexiblen und starrflexiblen ein- und doppelseitigen Leiterplatten sowie Multilayern. Einordnung nach Bohrstrategien, nach Montagetechnologien und nach Bestückungsebenen.

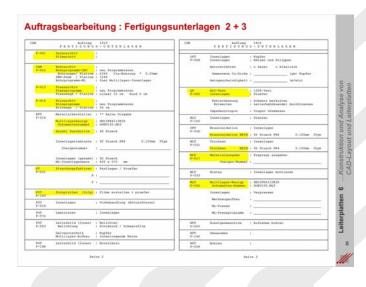

#### CAM-AV

CAM überprüft als einzige Instanz die Plausibilität aller vom CAD-Postprozeß erzeugten Daten und Dokumente.

Im Vorfeld hat der Design-Rule-Check die Aufgabe, die Produzierbarkeit der Leiterplatte zu überprüfen.

Die CAM-AV (= AuftragsVorbereitung) erstellt die Produktionsunterlagen für die Fertigung. Fehlende Unterlagen werden ergänzt, z. B. ein bemaßter Konturplan mit Referenz zum Bohrplan und/oder ein Multilayer-Bauplan. Dazu kommen die Daten für den AOI-Test und die Elektronische Prüfung sowie Coupons für diverse weitere Qualitäten der Leiterplatte/Baugruppe.

**Hinweis** Der CAM-Bereich des Leiterplattenherstellers ist der natürliche Partner des CAD-Designers.

#### CAM

Anforderungen an die CAM-Bearbeitung von Daten aus dem CAD-Postprozeß.

Design-Rule-Check und Prüfung auf Vollständigkeit der Dokumentation. Ergänzung fehlender Informationen und Daten für die fachgerechte Produktion von Leiterplatten.

## Logistik

Einblick in die Komplexität des Fertigungsprozesses von Leiterplatten.

Informationen zur Individualität der Produktionabläufe für Leiterplatten mit unterschiedlicher technischer Anforderung. Dokumentation von Fertigungsverfahren.

## **Fertigungsablauf**

Beschreibung der wichtigsten 16 Arbeitsschritte für die Herstellung eines realen 4-Lagen-Multilayers. Materialausgabe, Aufbringen des Fotolaminates, Leiterbildbelichtung, Verpressen, Bohren, Kontaktieren, Lötstopdruck, Endoberfläche und Konturfräsen.

#### Basismaterial: Grundbegriffe

Für die Fertigung von mehrlagigen Leiterplatten (~ Multilayern) werden Basismaterialien und Kupferfolien mit Prepregs zu einem Verbund verpresst. Dabei übernehmen die Prepregs die Funktion eines Klebers.

Prepregs

FR4-Kerne (doppelseitig mit Kupfer kaschiert)

Kupferfolien aussen

#### Begriffe

#### Innenlage

- ~ Innenlagenlaminat

- ~ Core (= Kern)

- ~ Multilayer-Innenlage

- ~ inner laver

#### **Basismaterial 1**

Kupferfolien, Prepregs und Basislaminate. Erläuterung der Grundbegriffe. Erklärung der Funktion der elementaren Materialkomponenten für den Bau einfacher Leiterplatten bis hin zu komplexen starrflexiblen Multilayern.

#### Basismaterial : Beispiele

#### RO-Material...

...der Fa. Rogers mit Blick auf die Fräskontur.

Das Material ist auf beiden Außenlagen mit einer Kupferfolie versehen. Der Kern des Materials ist sehr diffus.

Die stabilisierenden Gewebeeinlagen sind weitläufig und mit einem keramischen Füllstoff umgeben. Dadurch ist das Dielektrikum sehr homogen verteilt, mechanische Stabilität des Materials wird dadurch jedoch herabgesetzt.

#### Aramid

Doppelseitiges Basislaminat mit zwei – Einlagen aus Aramidgewebe und einer homogenen keramikhaltigen Füllung. Die dielektrikischen Werte liegen bei < 3 mit sehr gleichmäßiger Verteilung.

#### **Basismaterial 2**

Der innere Aufbau von Basismaterialien für die Produktion von Leiterplatten. Prozeßfähige Materialien für den Aufbau von starren, flexiblen und starrflexiblen Leiterplatten bis hin zu hochlagigen Multilayern. Eigenschaften von Füllstoffen und Harzen sowie Trägergeweben.

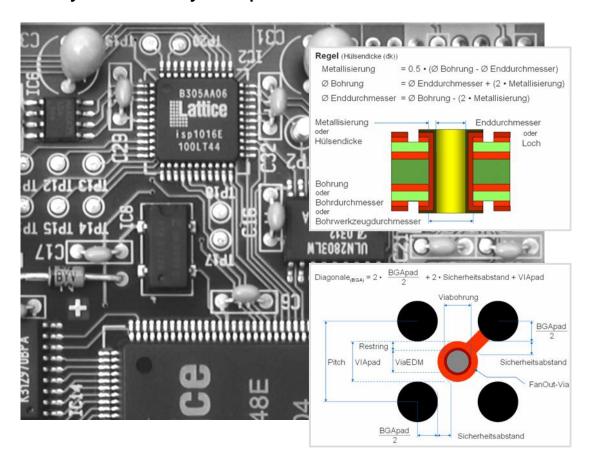

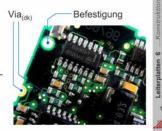

#### Bohrungen : Begriffe

Bohrungen ist der Überbegriff für alle Löcher, die während der Fertigung der Leiterplatte prozessiert werden.

#### Begriff

"Bohrung", "Loch" oder "Bohrloch" ist die Bezeichnung für alle THT-Bauteile und für Befestigungsbohrungen.

"Via" oder "Kontaktierung" ist die Bezeichnung für jede Art von Bohrungen, die ausschließlich Signalnetze verbindet. "Microvias" haben einen Enddurchmesser ≥ 50 und ≤ 100μm

#### **Bohrklassen**

Erläuterung der unterschiedlichen Bohrklassen und Bohrtypen, die bei der Konstruktion einer Baugruppe eingesetzt werden können.

Justagebohrungen für die Montage im Gehäuse, Verdrehschutz für die Bestückung. Varianten für dk- sowie Blind- und Buried Vias.

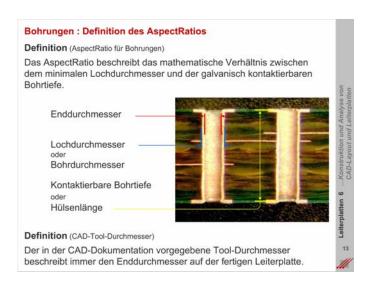

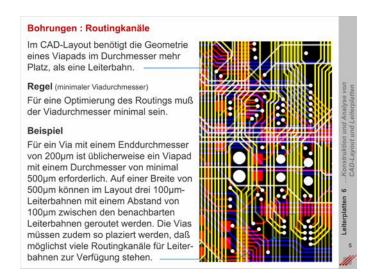

#### AspectRatio für Bohrungen

Erläuterung der Hintergründe für die wichtige Formulierung des Aspect-Ratios für Bohrungen.

Vorgaben für die Auswahl des Vias im Vorfeld der Erstellung des CAD-Layouts für eine Baugruppe. Definition und Berechnung des minimalen Viadurchmessers.

## Kontaktierungen

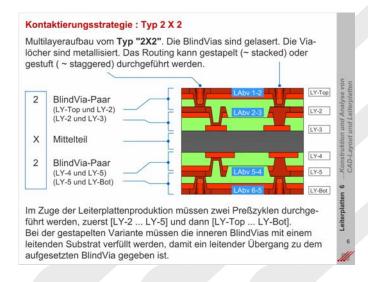

Kontaktierungsstrategien auf hochlagigen Multilayern mit Referenz zur Fertigungstechnologie.

Möglichkeiten der Lasertechnik bei der Konstruktion von Multilayern mit gestapelten und/oder gestuften BlindVias. Konventionell gebohrte BuriedVias, BlindVias und DKs.

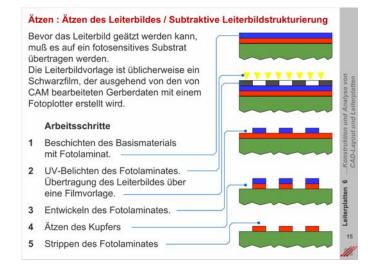

#### Leiterbild strukturieren

Belichten und Ätzen der Leiterbildstruktur. Vorgaben an das Layout. Definition des Ätzprofils über den Flankenwinkel. Formulierung eines AspectRatios für die Berechnung der Funktionsflächen bei SMDs. Einfluß des Flankenwinkels auf die Impedanz einer Leiterbahn.

#### Galvanotechnik

Kontaktierungsverfahren für das Einbringen von Kupfer in die Hülse von Bohrungen. Anforderungen an die Schichtdicke des Kupfers, die sich aus der Anwendung, der Funktion und der Bauteilmontage ergeben. Metallisieren von Leiterplattenkonturen und Höhenniveaus.

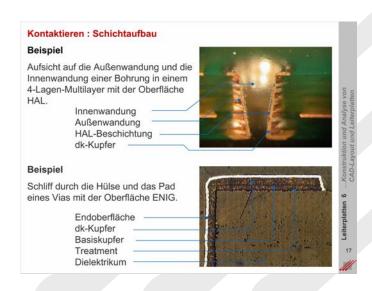

#### Metallisierungen

Abscheidung von Kupfer und galvanischen oder chemischen Oberflächen auf den Außenlagen von Leiterplatten. RoHs-Anforderungen. Schichtaufbauten und Schichtdicken für die üblichen Oberflächen HAL, ENIG (i.e. Chemisch Nickel/Gold) und Chemisch Zinn.

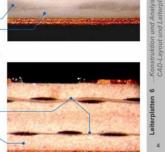

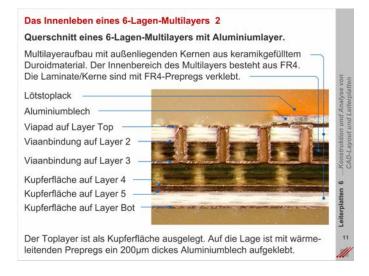

## Reale Lagenaufbauten

Analyse von Querschnitten durch reale Multilayer. Interpretation von Schliffbildern und Zuordnung der verbauten Materialien.

Möglichkeiten für die Konstruktion von Multilayern mit besonderen Materialien und Metallflächen.

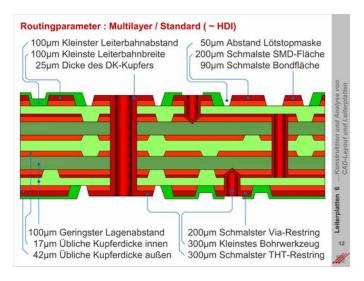

#### Routingparameter

Für Baugruppen mit der Komplexität "Standard", "HDI", "MFT", "UTM": Diverse Constraints für das Routing am CAD-System.

Parameter für Leiterbahnbreiten, Leiterbahnabstände, Freistellungen in der Lötstopmaske und Restringe für Vias und THT-Bohrungen.

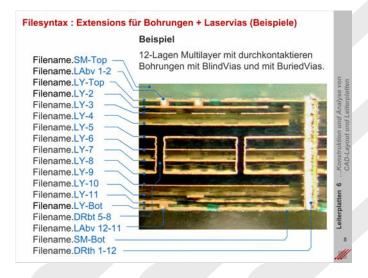

## **Filesyntax**

Anforderung an die Dokumentation von Produktionsdaten.

Vergabe von Extensions im Umfeld einer definierten Filesyntax.

Fileextensions für grafische (i.e. Leiterbild, Siebdruck) und mechanische (i.e. Bohren, Laser, Ritzen, Fräsen) Bearbeitungsschritte zur Produktion einer Leiterplatte.

| File-Inhalt                                                            | Funktion                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                        | Fortsetzung                                                                                                                                                                                                                                  |

| D14*                                                                   | Auswahl der 1. Aperture/Blende = D14                                                                                                                                                                                                         |

| G1X11000Y60000D2*                                                      | G1 = lineare Interpolation, Angabe der X + Y Koordinaten,<br>Funktion D2 = Licht aus, * = End Of Block (EOB)                                                                                                                                 |

| X11900Y60390D1*<br>X11900Y60590*<br>X11300Y60090D2*<br>X11300Y59890D1* | X + Y Koordinaten, Funktion D1 = ziehe eine Linie, * = EOB<br>Ziehe Linie bis X = 11900, Y = 60590 (fahre mit Licht)<br>Fahre ohne Licht an die Position X = 11300, Y = 60090<br>Ziehe eine Linie bis X = 11300, Y = 59890 (fahre mit Licht) |

| D30*<br>X29800Y60290D3*<br>X28050Y12290D3*<br>X19550Y60290D3*          | Wähle die Aperture/Blende D30<br>Blitze mit D30 ein Pad an Position X = 29800, Y = 60290<br>Blitze mit D30 ein Pad an Position X = 28050, Y = 12290<br>Blitze mit D30 ein Pad an Position X = 19550, Y = 60290                               |

| D47*<br>X13800Y8040D3*<br>X13800Y10040D3*<br>X35550Y60290D3*           | Wähle die Aperture/Blende D47<br>Biltze mit D47 ein Pad an Position X = 13800, Y = 8040<br>Biltze mit D47 ein Pad an Position X = 13800, Y = 10040<br>Biltze mit D47 ein Pad an Position X = 35550, Y = 60290                                |

| X0Y0D2*                                                                | Fahre ohne Licht auf die Nullposition X = 0 und Y = 0                                                                                                                                                                                        |

| M02*                                                                   | Ende der Datei Quelle : Mendritzki / Wiemers<br>LA-Seminar GERBER 2010                                                                                                                                                                       |

#### Gerberformat

Standardtransfer von Daten zur Produktion von Leiterplatten und Baugruppen.

Syntax des Gerberformates. Analyse von CAD-Layouts durch die systematische Interpretation von Gerberdaten während der CAM-Bearbeitung.

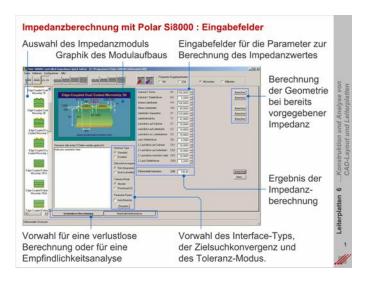

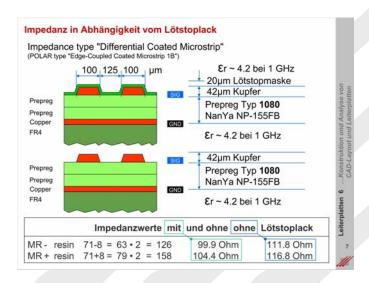

#### Impedanzberechnung

Erläuterung aller konventionellen Impedanzmoduln. SingleEnded für 50, 65 und 75 Ohm, Differentielle Impedanzen für 90 und 100 Ohm. Umsetzung typischer Impedanzwerte in geometrische Moduln für die Konstruktion von Multilayern. Eigene Berechnungen.

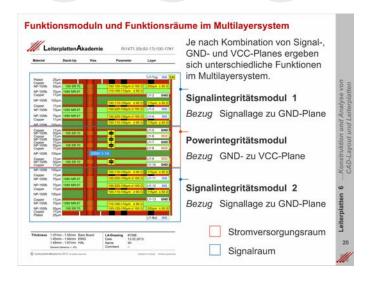

#### **Funktionsmodule**

Erforderliche Funktionsbereiche auf einer Leiterplatte aus physikalischer Sicht. Vorzudefinierende Räume innerhalb eines Lagenaufbaus für die diskrete Aufnahme von Signalen (z.B.: Differentielle Impedanzen) oder für den Einbau kapazitiver Stromversorgungssysteme.

##

#### **Funktionsmoduln**

Integration berechneter Funktionsmoduln für den Signaltransfer und die Stromversorgung in den Layer-Stackup des CAD-Systems. Formulierung des "Multilayersystems" mit einem komplexen Leistungsprofil, das alle Anforderungen der Baugruppe erfüllt.

Platz zur Verfügung stehen, um die differentiellen Leiterbahnpaare von

#### Highspeedprojekte

"Die Leiterplatte 2010" ist ein Referenzprojekt für die wohlüberlegte Entwicklung einer Highspeed-Baugruppe. Die Ergebnisse aus diesem Projekt sind hilfreich für das Konzept und die Planung einer anspruchsvollen Baugruppe, die wirtschaftliche und physikalische Bedingungen erfüllen muß.

#### Innenlagen: Beispiel 1 + 2

- Leiterbahnen

- Durch das Einbetten von Signalen ergeben sich isolierte Flächen. — Stromfluß und Rückstromwege sind nicht kontrolliert definiert.

der CPU zu den Steckern routen zu können.

- Die Impedanzreferenzen sind uneinheitlich. Es ergeben sich semicoplanare, coplanare und single ended Geometrien.

- 2 Viaplazierung

- Der Wert für "Viadistance" ist in den constraints (~ Routingvorgaben) zu klein vorgeben.

Die Freistellungen benachbarter Isolationspads gehen deshalb ineinander über und erzeugen Schlitze in der Powerplane. Der Stromfluß ist stark beeinträchtigt.

#### Signal- und Powerintegrität

Bewertung von Stromversorgungsflächen und Signalführungen. Nicht zu empfehlende Konstruktionen für das Routing von Layouts am CAD-System.

Einschränkungen der funktionalen Qualität eines CAD-Designs durch ungeeignete Routing-Constraints.

#### Crosstalk in der 3. Dimension

Den Abstand von Bildstrukturen zu berechnen, gehört zu den üblichen Aufgaben eines CAD-Systems. In der Fläche ist diese Aufgabe auf der Basis der Vektorkoordinaten und der konstruktiven Geometrien zu lösen. Für die Analyse im Raum ist die Kenntnis der Topologie des Multilayers absolut notwendig.

#### Beispiel

Der Abstand Leiterbahn zu Leiterbahn ist in der Ebene 440µm aber 125µm im Raum (= grün, LY-3 zu rot, LY-4).

#### Maßnahme

Die Signalräume im Lagenaufbau trennen und/oder die Leiterbahnen orthogonal routen.

#### Crosstalk

Analytische Bewertung des Routings von Signalleiterbahnen unter Beachtung der 3-Dimensionalität eines Multilayerlagenaufbaus. Berücksichtigung des Crosstalks in Z-Richtung.

Regeln für das Routen impedanzdefinierter Leiterbahnen.

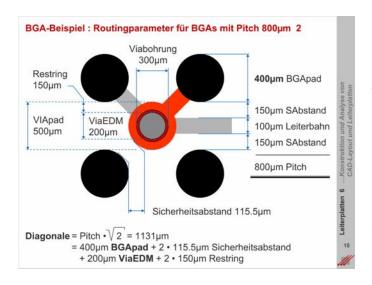

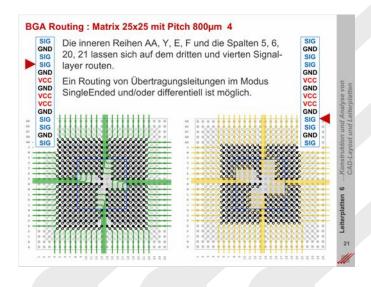

## Konstruktionsregeln für BGAs

Allgemeine Designprinzipien. Elementare Geometrien für die Konstruktion der BGA-Padstacks in der Bibliothek des CAD-Systems. Berechnung von Paddurchmesser, Sicherheitsabstand, Fan-Out-Via. Viadurchmesser und Leiterbahnbreite.

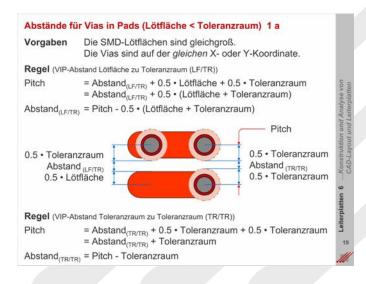

## Konstruktionsregeln für VIPs

Kalkulation der Geometrien für ein spezielles Routing im CAD-Layout. Berechnung von Abständen, Vias und Lötflächen für die Routingstrategie mit VIPs (i.e. ViasInPads). Erläuternde Beispielrechnungen und Übungsaufgaben für das Selbststudium.

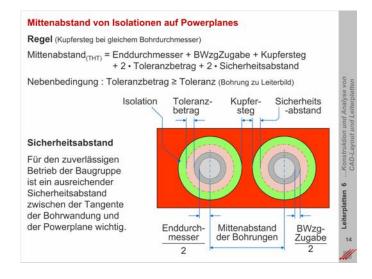

## Konstruktionsregeln für Planes

Berechnung von Grenzwerten für die Konstruktion von CAD-Layouts. Regeln für die Definition von Padstacks für Vias unter Beachtung der Rückstromwege auf Powerplanes bei Highspeed-Boards.

Ermittlung der Sicherheitsabstände.

#### Routingstrategie

Systematik bei der Planung der Leiterbahnführung in einem CAD-Layout.

Definierte Routingkanäle und Plazierung von Vias in Clustern. Optimale Nutzung von Flächen. Anforderungen an die Geometrie von Vias.

## **BGA-Routing**

Exemplarische Berechnung und Routing-Vorgabe für das Fan-Out eines BGAs mit einer Matrix von 25x25 Spalten und Reihen. Beispielhafte Verteilung der Signalplanes und der Powerplanes unter Berücksichtigung der Signal- und Powerintegrität.

## Multilayerbaupläne

Exemplarische Dokumentation von einfachen ein- und doppelseitigen Leiterplatten bis hin zu komplexen Multilayern.

Grafische Beschreibung des Aufbaus von Multilayersystemen.

Dokumentation elementarer physikalischer Eigenschaften.

12

#### Ihr Referent

**Arnold Wiemers** ist der Leiterplatte seit 1983 verbunden. Von 1985 bis 2009 war er bei der ILFA GmbH in Hannover beschäftigt.

Er war dort verantwortlich für die Fachbereiche CAD und CAM, für die Auftragsvorbereitung und für die technischen Dokumente der Firma ILFA im Internet.

Er ist seit 1982 freier Softwareentwickler (ISW), vornehmlich für branchentypische Applikationen im Bereich der Leiterplatte, wie die Kalkulation und die Fertigungssteuerung von Leiterplatten.

Diverse Fachveröffentlichungen. Referent für Seminare, Konferenzvorträge und Workshops zum Thema Leiterplattentechnologie (MFT, MPS, Impedanz, Multilayersysteme, Designregeln, Gerber, LP2010).

Vom IPC zertifizierter CID, CID+ und Instructor. FED-Designer und FED-Referent. Mitarbeit am Schulungskonzept des FED. Mitarbeit in der international besetzten "Projektgruppe Design" des FED und des VdL/ZVEI.

## Die Leiterplatten Akademie

Die Sicherung des Standortes Deutschland in Europa und der Erhalt der internationalen Wettbewerbsfähigkeit setzt sowohl die systematische als auch die kontinuierliche Qualifikation der Mitarbeiter/innen eines Unternehmens voraus.

Die wirtschaftliche Leistungsfähigkeit einer Industriegesellschaft und ihre technologische Kompetenz am Weltmarkt wird (auch) durch die Qualität ihrer Elektronikprodukte bestimmt.

Das erfordert eine fachlich hochwertige Aus- und Weiterbildung.

Die zentrale Aufgabe der LeiterplattenAkademie ist, das Fachwissen aus den Bereichen der Schaltungsentwicklung, des CAD-Designs, der CAM-Bearbeitung, der Leiterplattentechnologie und der Baugruppenproduktion in Seminaren, Workshops und Tutorials zu vermitteln.

13

#### Seminare und Teilnahmegebühren

Das Seminar/Tutorial ist **1-wöchig**, beginnt am Montag und endet am Freitag. Erforderliche Softwareprogramme werden für die Dauer des Seminars von uns zur Verfügung gestellt.

Wir schulen in Deutschland, Österreich und der Schweiz.

#### Hochschulseminare

Das Seminar/Tutorial "Leiterplatten 72 ...Konstruktion und Analyse von CAD-Layouts und Leiterplatten" wird in Kooperation mit Hochschulen durchgeführt.

Gäste aus der Industrie sind herzlich willkommen.

#### Freies Seminar/Tutorial

Die Durchführung liegt bei der LeiterplattenAkademie. Die Termine werden via Mailing, eMail, Internet oder Presseveröffentlichungen mitgeteilt. Die Teilnahmegebühr beträgt 1.860,00 € zzgl. MwSt. pro Person. Enthalten sind ausführliche Seminarunterlagen sowie ein Zertifikat.

#### InHouse: Unser Seminar in Ihrem Haus

Das Seminar/Tutorial "Leiterplatten 72 ...Konstruktion und Analyse von CAD-Layouts und Leiterplatten" wird von uns auch InHouse referiert. Sie sparen Teilnahmegebühren sowie Reise- und Übernachtungskosten. Für 5.800,00 €zzgl. MwSt. kommt unser Referent zu Ihnen ins Haus bei einer Teilnahme von 4 Personen. Für mehr/weniger als 4 Teilnehmer unterbreiten wir Ihnen gerne ein angepaßtes Angebot.

Jeder Teilnehmer erhält ausführliche Seminarunterlagen sowie ein Teilnahmezertifikat.

Eine individuelle Themengestaltung mit firmentypischen Schwerpunkten ist selbstverständlich möglich. Bitte stimmen Sie sich mit uns ab.

## Die LeiterplattenAkademie

Die LA - LeiterplattenAkademie GmbH ist eine Schulungsund Weiterbildungseinrichtung für die Fachbereiche

Schaltungsentwicklung

**CAD-Design**

**CAM-Bearbeitung**

Leiterplattentechnologie

Baugruppenproduktion

Die Akademie versteht sich als Partner für öffentliche Einrichtungen und Unternehmen der Wirtschaft, die in vergleichbaren Feldern engagiert sind.

## LA - LeiterplattenAkademie GmbH Krefelder Straße 18 10555 Berlin

Telefon (030) 34 35 18 99 Telefax (030) 34 35 19 02

eMail info@leiterplattenakademie.de lnternet www.leiterplattenakademie.de