# **Fachtagung**

13. + 14. Februar 2019 in Blaubeuren

#### **Arnold Wiemers**

Berechnung von Lötflächen und Lötvolumina mit Blick auf die Rückätzung des Leiterbildes während der Leiterplattenproduktion

Geometrie von Leiterbildern

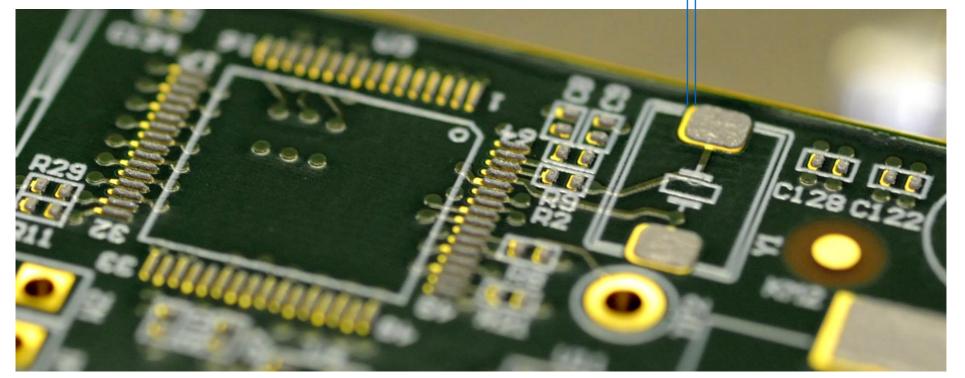

#### Geometrien für SMD-Komponenten

#### Lötflächen

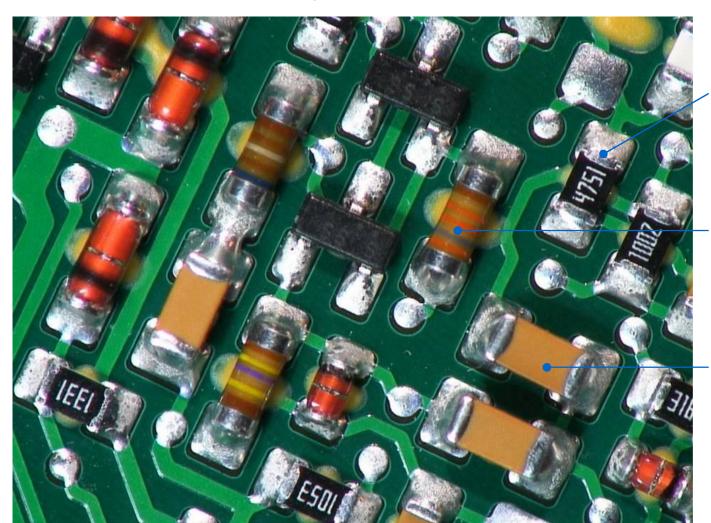

Die Verbindung zwischen den SMD-Komponenten und der Leiterplatte muß durch den Lötprozeß gewährleistet werden. Bei Bauformen > 0402 ist der Aufdruck von Lotpaste mit einer Metallschablone unkritisch.

Bauform 0805 2.00x1.25mm

Bauform Minimelf 3.60x1.40mm

Bauform 1206 3.20x1.60mm

#### SMD-Bauformen: 2-polig

Für Widerstand, Kondensator und Diode ist die 2-polige Bauvariante (noch) typisch. Um Platz, Bauhöhe und Gewicht zu sparen, sind die Grundflächen dieser Komponenten kontinuierlich reduziert worden.

| Faktor                                            | Beispiel | Bauform      | Abmaße                                | Grundfläche               |

|---------------------------------------------------|----------|--------------|---------------------------------------|---------------------------|

| $\frac{06 \cdot 03}{02 \cdot 01} = 9\text{-fach}$ |          | 0603<br>0201 | • • • • • • • • • • • • • • • • • • • | 1161288µm² —<br>129032µm² |

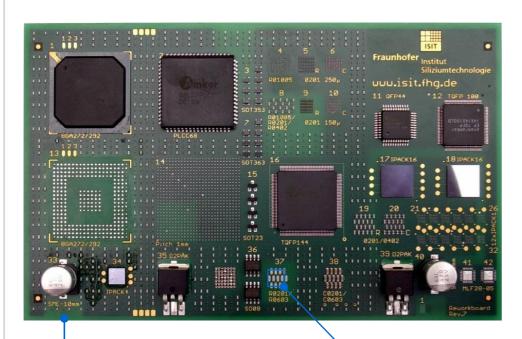

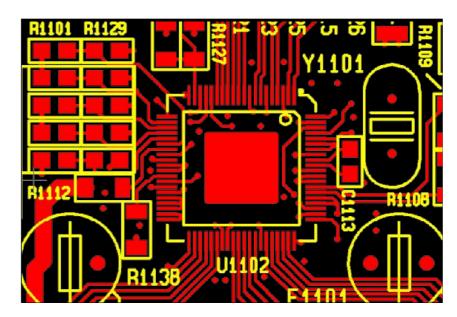

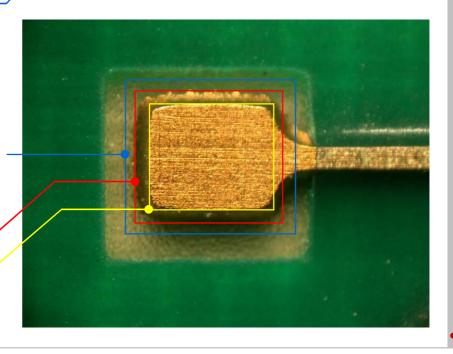

Fraunhofer / ISIT: Reworkboard

#### Rückätzung des Leiterbildes

#### Reduzierung der Leiterbildgeometrie

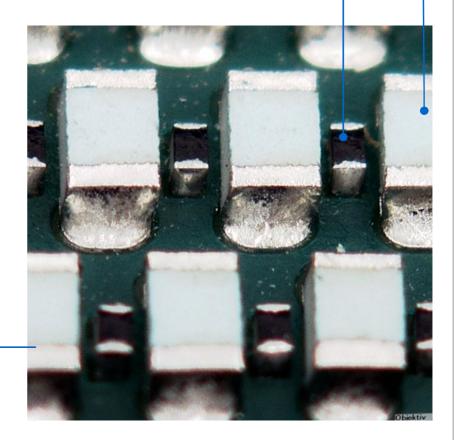

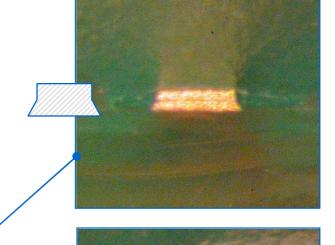

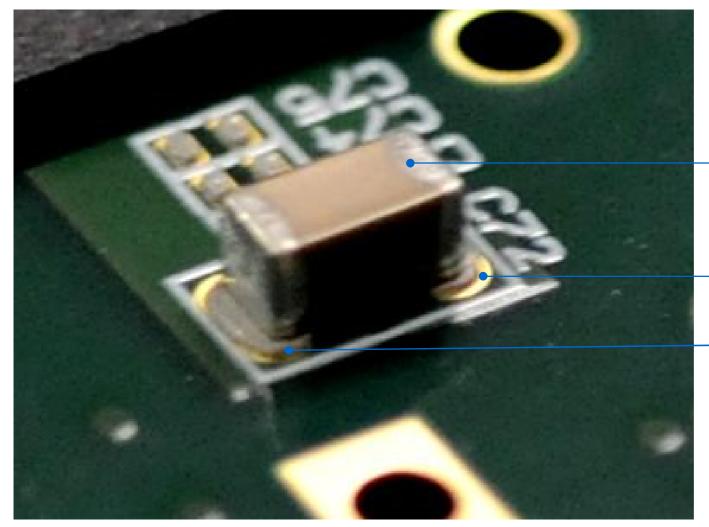

Der Ätzmechanismus unterscheidet nicht zwischen den Leiterbahnen und den Lötflächen. In Leiterbahnen werden die Übertragungseigenschaften beeinfluß, auf SMD-Flächen die Lötverbindungen beim Lotaufschmelzen.

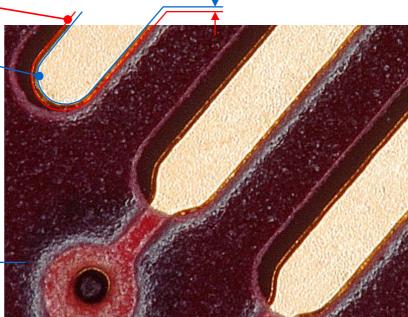

Via-Restring auf einer Außenlage mit 42µm Kupfer.

SMD-Lötfläche. Es gibt keine Lötung an den Flanken der Lötfläche.

#### **Erwartete Querschnittsprofile**

Allgemein wird angenommen, daß die Querschnitte von Bildstrukturen idealerweise eckig sind. In der Praxis ist das jedoch nicht so.

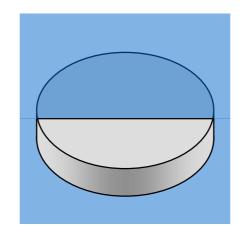

#### **Querschnitt / Pad**

Pad für Via, THT-Bauteile und BGAs

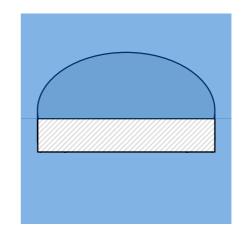

#### **Querschnitt / Vektor**

SMD-Pad oder Leiterbahn-Vektor

#### **Erwartung und Irrtum**

#### Illusionen

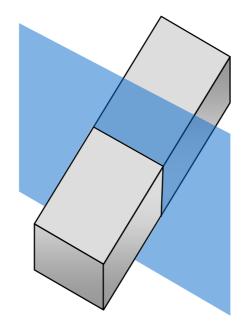

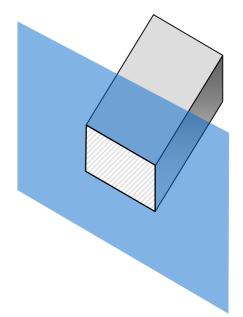

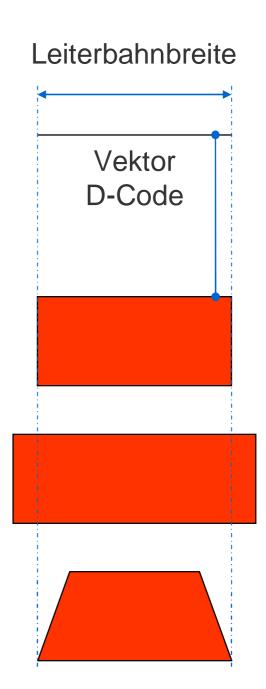

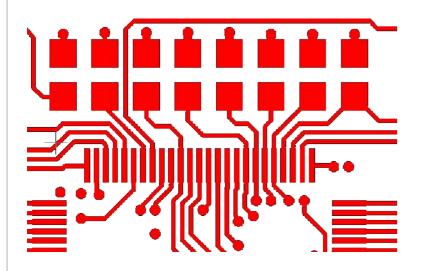

In der *virtuellen* Welt des *CAD*-Systems ist das Leiterbild mit seiner späteren Sollbreite 1-dimensional angelegt (D-Code). Ergänzt um die 1-dimensionale Vektor-Information werden die Produktionsdaten über den Postprozeß 2-dimensional exportiert.

Es wird stillschweigend unterstellt, daß auf der Leiterplatte daraus eine 3-dimensionale Rechteckstruktur wird.

In der *virtuellen* Welt des *CAM*-Systems werden die 2-dimensionalen Daten eingelesen. Die zu erwartenden Verluste an der Breite der Bildstruktur werden kompensiert.

Das *reale* Leiterbild ist 3-dimensional und hat trapezoidale Querschnitte.

#### Leiterbilder nach dem Ätzen

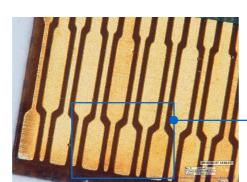

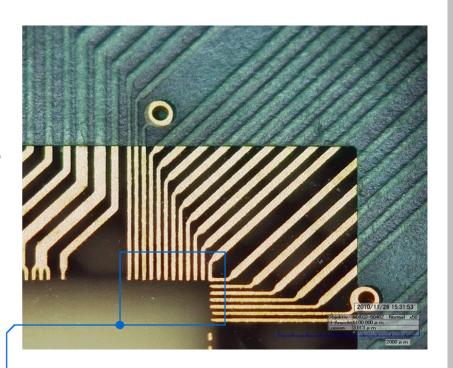

Beispiel (Ätzen ZIF-Stecker)

ZIF-Stecker auf flexiblem Polyimidmaterial. Nach dem Ätzen ist der Unter-

schied in der Breite der Geometrie im Kupfer erkennbar.

Soll Vorgabe seitens CAD/CAM

Ist Geometrie nach dem Ätzen

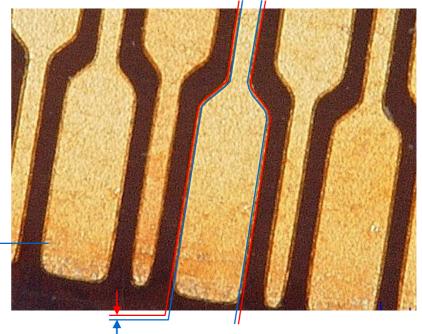

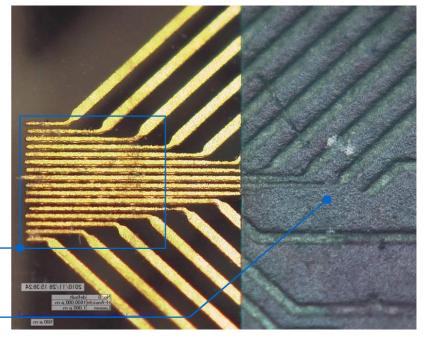

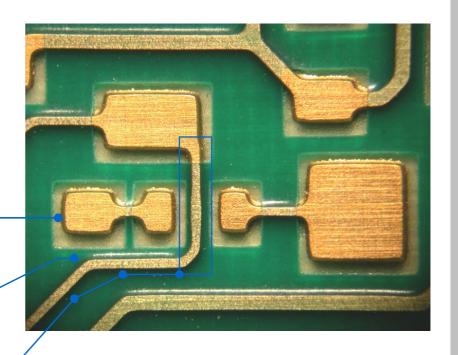

Beispiel (Ätzen SMD-Stecker)

Die Grundfläche im Aufsetzbereich der Steckerpads sind nach dem Ätzen sichtbar reduziert.

# Ätzen: Hintergründe

Die elektrisch leitenden Lagen einer Leiterplatte sind vor Beginn der Strukturierung des Leiterbildes vollflächig aus Kupfer. Die Ausprägung des Leiterbildes erfolgt mit einer subtraktiven Strategie. In einem Sprühverfahren wird ein Ätzmedium aufgebracht, mit dem das nicht benötigte Kupfer entfernt wird. Die spätere Leiterbildstruktur muß während des Ätzprozesses mit einem Resist (= Schutz) abgedeckt sein.

Die Technologie des Sprühverfahrens und die Strömungseigenschaften des Ätzmediums führen zur *Unter-*

ätzung des Leiterbildes unterhalb des Resistes. Es bilden sich trapezförmige Querschnittsprofile aus.

Unterätzung

#### Rückätzung

# Kompensation der Ätzverluste

Wegen der Rückätzung wären alle Bildstrukturen nach dem Ätzen zu schmal. Um das zu kompensieren, werden von CAM während der Bearbeitung alle Fotowerkzeuge für die Belichtung *skaliert* (~ ...kupferdickenabhängige Blendenkompensation).

Vektor D-Code

Verlust durch Rückätzung -

Kompensation von CAM

# Rückätzung und Unterätzung

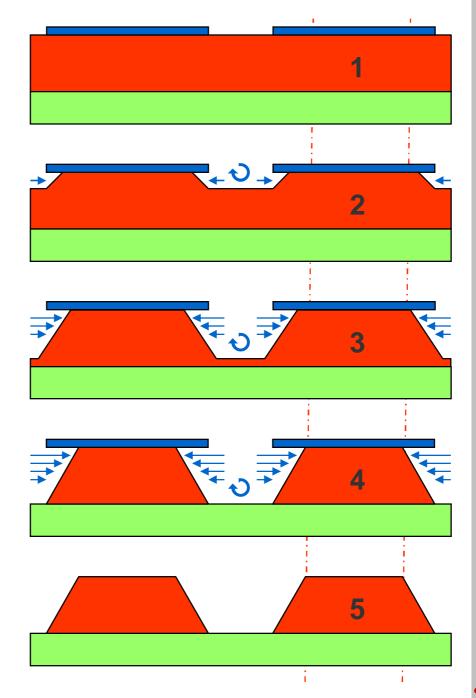

#### Subtraktiver Ätzmechanismus: Fotoresist

- Fotolaminat

- Basiskupfer

- Dielektrikum

- **→** Ätzmedium

# Ätzen (Fotolaminat als Ätzresist)

- 1) Laminieren und Belichten des Fotolaminates.

- 2) Ätzen der Kupferschicht. Während

- 3) des Ätzens in die Tiefe hin zum

- 4) Dielektrikum wird auch unterhalb des Fotolaminates Kupfer von den Flanken der Bildstruktur geätzt.

- 5) Die fertige Bildstruktur zeigt den typischen trapezartigen Querschnitt.

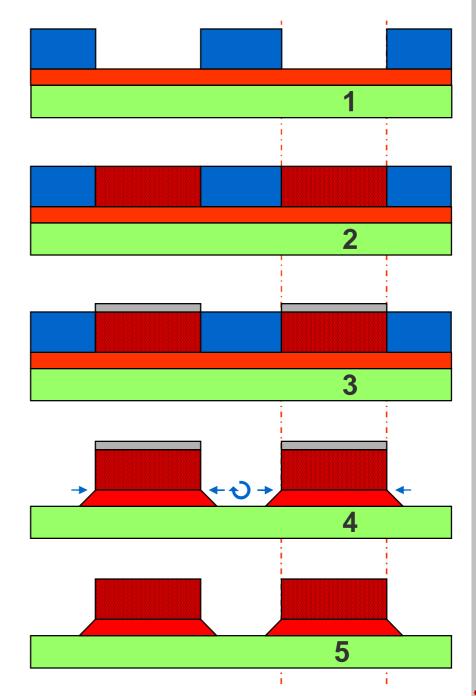

# **Unterätzung: Semiadditiver Ätzmechanismus**

- Metallresist

- Fotolaminat

- Basiskupfer

- dk-Kupfer

- Dielektrikum

- → Ätzmedium

## Ätzen (Foto- und Metallresist)

- 1) Laminieren und Belichten des Fotolaminats.

- 2) Kupferaufbau.

- 3) Metallresist aufbauen.

- 4) Fotolaminat strippen. Kupfer ätzen.

- 5) Die fertige Bildstruktur zeigt den ätzbedingten Trapezquerschnitt nur im Bereich des Basiskupfers.

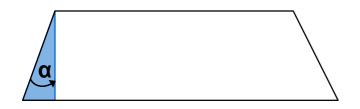

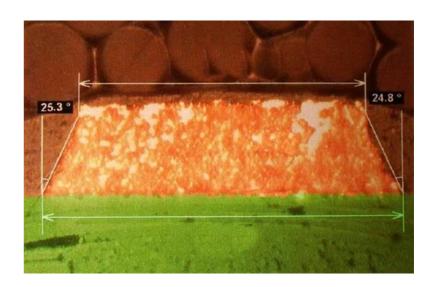

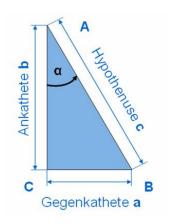

# Querschnittsprofil

#### **Querschnittsprofil: Allgemein**

# Subtraktiver Ätzprozeß

Querschnittform Trapez

Flankenwinkel α 25°

# Semiadditiver Ätzprozeß

Querschnittform Trapez

Flankenwinkel α 15°

Werkbilder ILFA / Modifikation Wi

Regel (Querschnittsprofil)

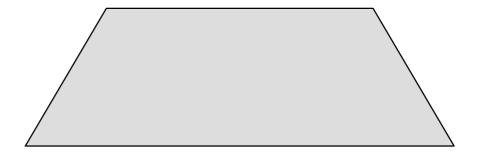

Das Querschnittsprofil einer Leiterbahn, oder ganz allgemein das Querschnittsprofil einer Bildstruktur, ist *immer tendenziell* ein Trapez.

# **Querschnittsprofil: Profilvarianten**

Das Querschnittsprofil einer Leiterbahn auf einer kontaktierten Lage ist anders, als das Querschnittsprofil einer Leiterbahn auf einer nicht kontaktierten Lage.

Die Winkel auf der rechten und der linken Ätzflanke einer Leiterbildstruktur sind nicht immer identisch.

## **Querschnittsprofil: Grundregeln**

Regeln (Querschnittsprofil)

Das elementare Querschnittsprofil eines Leiterbildes ist *nicht* von der Breite des Leiterbildes abhängig sondern nur von der Ätztechnologie und von der Kupferdicke auf der jeweiligen Lage einer Leiterplatte.

Das Profil hat auf ein *breiteres* Leiterbild mit geringer Kupferdicke einen geringen Einfluß und kann praktisch vernachlässigt werden.

Für ein sehr *schmales* Leiterbild und/oder für Leiterbilder mit großer Kupferdicke müssen die Auswirkungen des Querschnittsprofils auf die physikalischen Eigenschaften berücksichtigt werden.

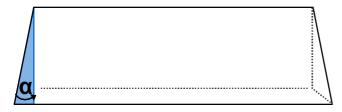

#### Vorgabe (Querschnittsprofil)

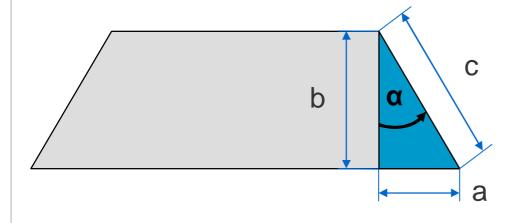

Das Querschnittsprofil eines Leiterbildes wird vereinfacht als *gleich-schenkliges Trapez* angenommen.

# Tangens Alpha

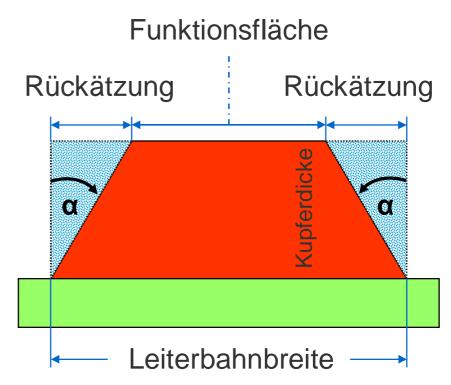

## **Querschnittsprofil: Definition des Tangens Alpha**

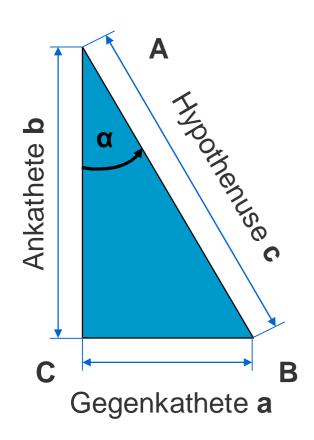

Die Längen für a, b und c sind nicht ohne weiteres ermittelbar. Die Dokumentation der CAD-Daten gibt dazu keine Auskunft.

Eine Beziehung zwischen diesen Größen kann über die **trigonometrische Definition** des Tanges beschrieben werden.

Allgemein gilt:

tan

$$\alpha = \frac{\text{Gegenkathete}}{\text{Ankathete}} = \frac{a}{b}$$

Gegenkathete = Ankathete • tan  $\alpha$  $a = b • tan \alpha$

Alpha 'α' ist der Winkel zwischen der Flanke 'c' der Bildstruktur und der Kupferdicke 'b'.

Mit dem Tangens des Winkels α wird ein mathematischer Zusammenhang zwischen der Rückätzung und der Kupferdicke formuliert.

Regel (Rückätzung gesamt)

Rückätzung<sub>(ges)</sub> = 2 • Kupferdicke • tan  $\alpha$

Daraus ergibt sich:

Regel (Abhängigkeit der Rückätzung)

Die Rückätzung ist ausschließlich von der Kupferdicke abhängig.

Begriff (Funktionsfläche)

Die Breite des oberen Leiterbildes wird als *Funktionsfläche* bezeichnet.

Regel (Funktionsfläche)

Funktionsfläche = Leiterbahnbreite - Rückätzung<sub>(ges)</sub> = Leiterbahnbreite - (2 • Kupferdicke • tan α)

#### Tangens Alpha: Werte 6

#### **Beispiel**

Bei einem Winkel von 15° und einer Kupferdicke von 37 µm ist die Bildstruktur auf der Oberseite 19.8 µm schmaler als an der Basis.

| Tangens                         | Gegenka<br>Ankathete |                | Gegenkathete<br>Ankathete <b>42</b> µm |                |  |

|---------------------------------|----------------------|----------------|----------------------------------------|----------------|--|

| $tan 0^{\circ} = 0$             | 0 µm                 | 0 µm           | 0 µm                                   | 0 µm           |  |

| tan 15° ≈ 0.2679                | <b>9.9 μm</b>        | <b>19.8 μm</b> | <b>12.6 μm</b>                         | <b>22.5 μm</b> |  |

| tan 20° ≈ 0.3640                | 13.5 μm              | 26.9 μm        | 15.3 μm                                | 20.6 μm        |  |

| tan 25° ≈ 0.4663                | 17.3 μm              | 34.5 μm        | 19.6 μm                                | 39.2 μm        |  |

| tan 30° ≈ 0.5774                | 21.4 μm              | 42.7 μm        | 24.3 μm                                | 48.5 μm        |  |

| tan 35° ≈ 0.7002                | 24.5 μm              | 49.0 μm        | 29.4 μm                                | 58.8 μm        |  |

| tan 40° ≈ 0.8391                | 31.5 μm              | 62.1 μm        | 35.2 μm                                | 70.5 μm        |  |

| $tan 45^{\circ} = 1.0000$       | 37.0 μm              | 74.0 μm        | 42.0 μm                                | 84.0 μm        |  |

| $tan 60^{\circ} \approx 1.7321$ | 64.1 μm              | 128.2 μm       | 72.8 μm                                | 145.5 μm       |  |

| $tan 70^{\circ} \approx 2.7475$ | 101.7 μm             | 203.3 μm       | 115.4 μm                               | 230.8 μm       |  |

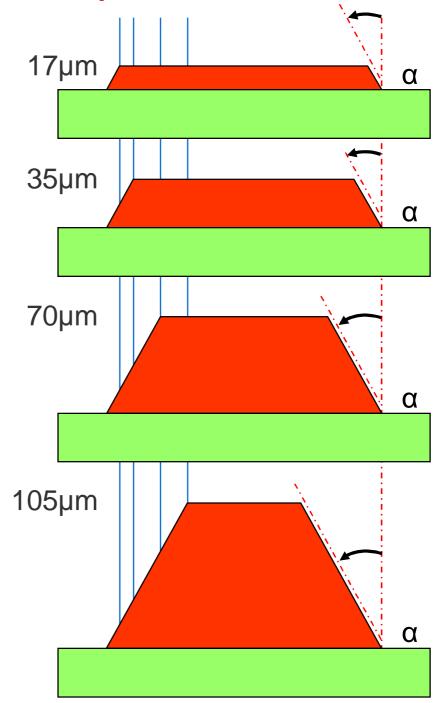

# Funktionsfläche

#### Funktionsfläche: Abhängigkeit von der Kupferdicke

Beispiel (Kupferdicke und Entwärmung)

Die Funktionsfläche wird schmaler, wenn die Kupferdicke zunimmt. Die Voraussetzung ist, daß der Ätzwinkel α gleichbleibt.

Es ändert sich dann aber auch die Qualität des Leiterbahnquerschnitts.

Wenn die Funktionsfläche für die Montage von Bauteilen vorgesehen ist, dann muß eine Kompensation in der CAD-Bibliothek vorgenommen werden.

Wenn das Leiterbild für die Entwärmung der Baugruppe benötigt wird, dann muß der Volumenverlust berechnet werden.

Ebenfalls beachtet werden muß die Stromtragfähigkeit der Leiterbahnen.

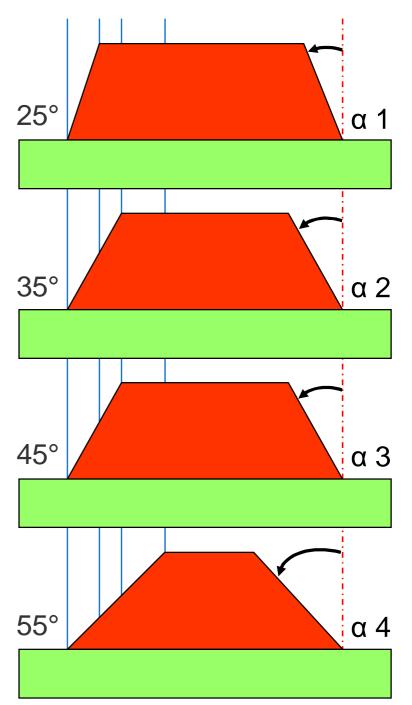

#### Funktionsfläche: Abhängigkeit vom Ätzwinkel

Beispiel (Ätzwinkel und Bestückung)

Die Funktionsfläche wird schmaler, wenn der Ätzwinkel α zunimmt. Die Voraussetzung ist, daß die Kupferdicke gleichbleibt.

Eine Änderung des Ätzwinkels führt direkt zu einer Änderung der Breite der Funktionsfläche.

Schwankungen im Ätzprozeß wirken sich deshalb auf den Lötmeniskus während der Baugruppenproduktion aus.

Durch den Ätzwinkel ändert sich der Querschnitt der Leiterbahnen. Das verändert die Wärmeabstrahlung. Die veränderte Kapazität wiederum beeinflußt über die Impedanz die Signallaufzeit.

## Rückätzung: Prozessierbarkeit von Funktionsflächen

**Begriff** (UFT)

UFT steht für UltraFinelineTechnology. Damit werden Leiterbildbreiten und Leiterbildabstände von ≤ 75µm bezeichnet.

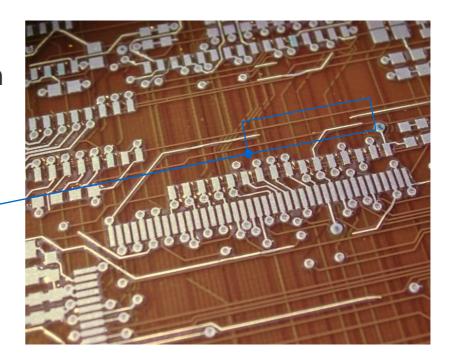

## Beispiel (UFT-Leiterbilder)

Die Leiterplatte soll Chips aufnehmen. Der Kontakt zur Leiterplatte soll über Leitkleben hergestellt werden. Die Kupferschichtdicken liegen bei ca. 29µm (~ 9µm Basiskupfer plus 20µm dk-Kupfer).

Die Leiterbahnen sind mit Strukturen von 65µm im Grenzbereich (oben).

Die Leiterbahnen mit 50µm Strukturen können mit üblicher Ätztechnik nicht mehr prozessiert werden (unten).

Als Folge von Ätzfehlern gibt es viele Kurzschlüsse und Unterbrechungen

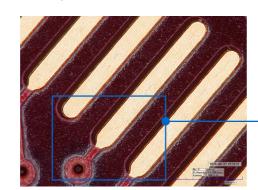

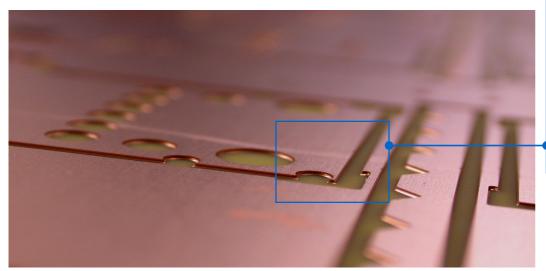

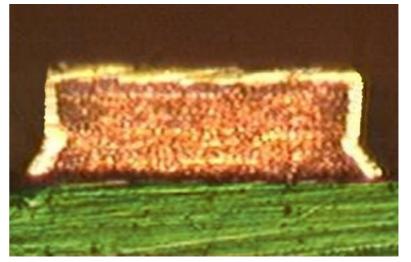

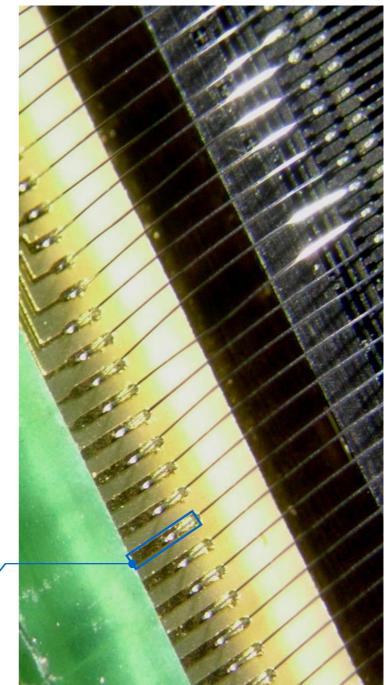

#### Rückätzung: Reduzierung der Funktionsfläche

Beispiel (Dickkupfer 105µm)

Die Leiterplatte hat auf den Außenlagen eine Kupferdicke von 130µm (~ 105µm Basiskupfer plus 25µm dk-Kupfer).

Die Leiterbahnen mit einer Breite von 250µm sind nicht zuverlässig herstellbar. Das Ätzen (...mit *Fotoresist*) führt zu erheblichen Beschädigungen des Leiterbildes.

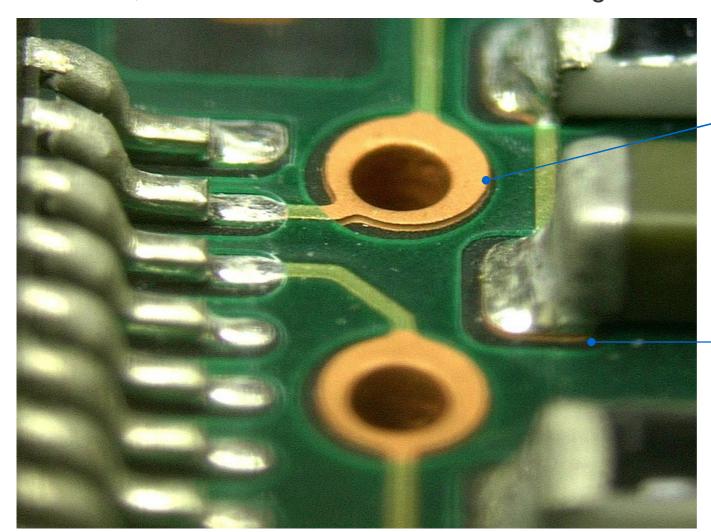

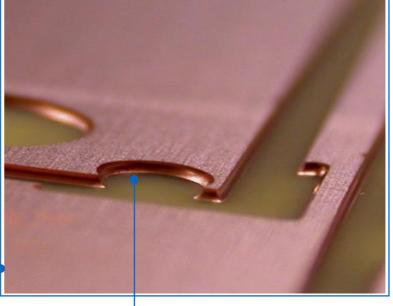

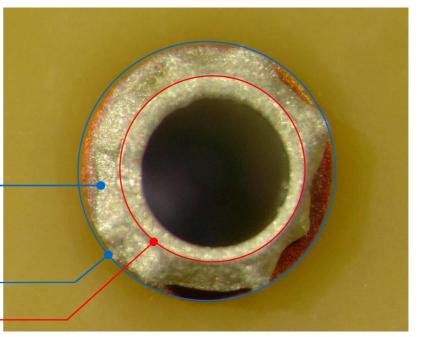

#### Beispiel (Dickkupfer 210µm)

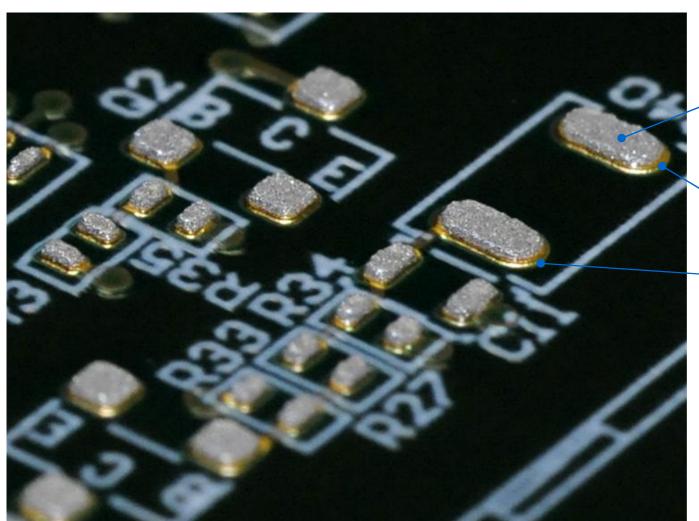

Sicht auf das Pad eines Vias mit einer Kupferoberflächendicke von ca. 235µm (~ 210µm Basiskupfer plus 25µm dk-Kupfer).

Unterhalb des *Metallresists* ist das Kupfer stark zurückgeätzt. Von der Padbreite aus der CAD-Bibliothek ist nur noch 1/3 übrig.

#### Rückätzung: Reduzierung der Funktionsfläche

Regel (Rückätzung)

Es gibt immer eine Rückätzung der Leiterbildstruktur.

CAD-Systeme bilden das spätere Layout 2-dimensional ab und kennen keine Rückätzung. Alle Leiterbildstrukturen sind aber ihrer Natur gemäß 3-dimensional.

Weil die Unterseite die Referenz für die Sollbreite einer Bildstruktur sein *muß*, ergibt sich, daß die Breite einer Bildstruktur auf ihrer Oberfläche *niemals* identisch ist mit der deklarierten Breite der originären Vektorstruktur am CAD-System.

#### Regel (Lötflächendurchmesser)

Die Geometrie einer Funktionsfläche ist in der Praxis *immer* um den Betrag der Rückätzung kleiner, als vom CAD-System vorgegeben.

#### Einbindung der Rückätzung in die CAD-Bibliotheksdefinitionen

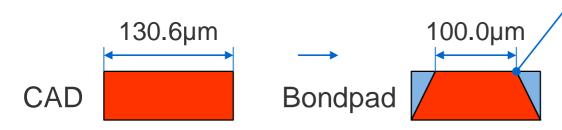

#### **Aufgabe**

Eine Bondfläche soll auf der Oberfläche eine Breite von minimal 100 µm haben.

#### Vorgaben

Die Kupferdicke beträgt 42 µm. Der Ätzwinkel liegt bei 20°.

#### Lösung

Bedingt durch die Rückätzung beträgt bei diesen Vorgaben die Reduzierung der Padbreite 30.6 µm.

In der Bibliothek des CAD-Systems muß daher das Bondpad mit einer Breite von  $100 \ \mu m + 30.6 \ \mu m = 130.6 \ \mu m$  angelegt werden.

## Leiterbildabstand: Dickkupfer (Details)

#### Konturen

Die Konturenschärfe von Leiterbildern nimmt ab, wenn die Kupferschichten dicker werden. Durch den länger anhaltenden Angriff des Ätzmediums werden die Kanten von rechteckigen — Pads abgetragen. Leiterbahnen werden bei Richtungswechseln abgerundet. —

Die layoutbedingte Verteilung des Ätzmediums auf der Oberfläche führt zu – ungleichmäßig dicken Leiterbildern.

#### Lötfläche

Die in der CAD-Bibliothek vorgesehene Lötfläche wird drastisch reduziert.

Verantwortlich dafür sind die fehlende Blendenkompensation und die Rückätzung des (...freiliegenden) Pads.

#### SMD-Lötfläche: Einfluß des Ätzwinkels 1

#### Beispiel

Bei einer Kupferdicke von 42µm und einer SMD-Lötfläche von 400x1000µm entspricht ein Winkel von 15° für die Ätzflanke einem Flächenverlust von 7.7 %.

| Kupferdicke<br>Tangens<br>Rückätzung | <b>42μm</b><br><b>15°</b> ( ~ 0.268)<br><b>22.50μm</b> | ) | 25° ( ~ 0.466<br>39.17μm | 6) | 35° ( ~ 0.7)<br>58.82µm |    |

|--------------------------------------|--------------------------------------------------------|---|--------------------------|----|-------------------------|----|

| SMD-Lötfläche                        | Flächenverlust                                         | F | lächenverlust            | F  | -<br>lächenverlus       | t_ |

| 300x1500µm                           | 8.9 %                                                  |   | 15.3 %                   |    | 22.8 %                  |    |

| 300x2000µm                           | 8.5 %                                                  |   | 14.8 %                   |    | 22.0 %                  |    |

| 350x2000µm                           | 7.5 %                                                  |   | 12.9 %                   |    | 19.3 %                  |    |

| 350x3000µm                           | 7.1 %                                                  |   | 12.4 %                   |    | 18.4 %                  |    |

| 400x1000μm                           | 7.7 %                                                  |   | 13.3 %                   |    | 19.7 %                  |    |

| 400x2500µm                           | 6.5 %                                                  |   | 11.2 %                   |    | 16.7 %                  |    |

| 400x3000µm                           | 6.3 %                                                  |   | 11.0 %                   |    | 16.4 %                  |    |

| 400x3500µm                           | 6.2 %                                                  |   | 10.8 %                   |    | 16.1 %                  |    |

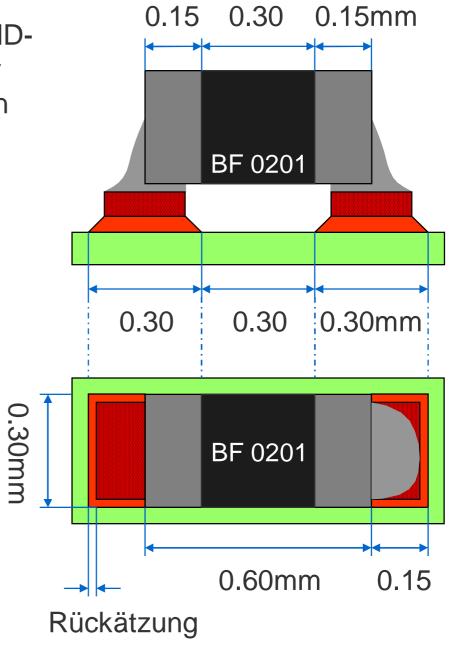

#### Rückätzung: Reduzierung der Lötfläche/Funktionsfläche

#### **Aufgabe**

Wie groß ist die Lötfläche bei einer SMD-Bauform vom TYP "0201", wenn in der CAD-Bibliothek eine Padgeometrie von 300µm x 300µm vorgesehen ist ?

#### Vorgaben

Die Kupferdicke beträgt 42µm. Der Ätzwinkel liegt bei 20°.

#### Lösung

Die Rückätzung beträgt bei diesen Vorgaben umlaufend 30.58µm. Die Lötfläche des Pads wäre dann 269.42µm x 269.42µm. Das entspricht einer Reduzierung der Fläche um 19.3 %.

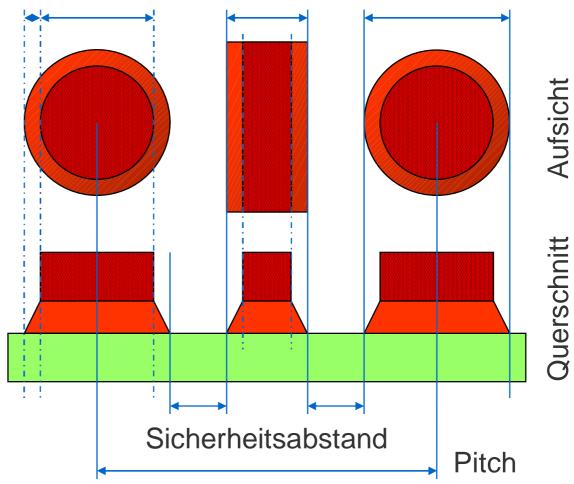

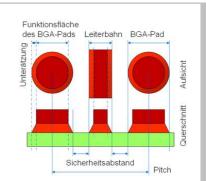

#### **BGA: Grund- und Funktionsfläche**

Regel (Funktionsfläche BGA)

Funktionsfläche<sub>(BGA)</sub> = BGApad - Rückätzung<sub>(ges)</sub>

= BGApad - 2 • Kupferdicke • tan α

Funktionsfläche

des BGA-Pads Rückätzung

#### **Hinweis**

Der Sicherheitsabstand im CAD-Layout entspricht in der Praxis dem Abstand der Bildstrukturen auf der Höhe der Dielektrikums.

Für BGA-Pads entspricht die Funktionsfläche für das Aufsetzen der Balls der Vorgabe aus der CAD-Bibliothek verringert um den Betrag für die Rückätzung.

Leiterbahn

BGA-Pad

#### BGA-Paddurchmesser: Einfluß des Ätzwinkels

#### Beispiel

Bei einer Kupferdicke von 42µm und einem Paddurchmesser von 400µm entspricht ein Ätzwinkel von 15° für die Ätzflanke einem Flächenverlust von 10.9 % für die BGA-Oberfläche.

| Rückätzung                                                                  | 22.50µm                                              |  | 25° ( ~ 0.466<br>39.17μm                                | 5) 35° ( ~ 0.7)<br>58.82µm                              |

|-----------------------------------------------------------------------------|------------------------------------------------------|--|---------------------------------------------------------|---------------------------------------------------------|

| Paddurchmesser Flächenverlust                                               |                                                      |  | lächenverlust                                           | Flächenverlust                                          |

| 200μm<br>250μm<br>300μm<br>350μm<br><b>400μm</b><br>450μm<br>500μm<br>550μm | 21.2 % 17.2 % 14.4 % 12.4 % 10.9 % 9.8 % 8.8 % 8.0 % |  | 35.3 % 28.9 % 24.4 % 21.1 % 18.6 % 16.7 % 15.1 % 13.7 % | 50.2 % 41.5 % 35.4 % 30.8 % 27.2 % 24.4 % 22.1 % 20.2 % |

# Lotpastendruck

#### Lotpastendruck

#### **Toleranz**

Lotpaste wird üblicherweise im Siebruckverfahren aufgebracht.

**Regel** (Toleranz Lotpastendruck)

Der maximal zulässige Versatz des Lotpastenpads zum SMD-Pad ist ± 100µm für Bauformen ≥ 0402. Der maximale Versatz für Bauformen ≤ 0201 ist ± 50µm.

Versatz

Bild: Rainer Taube

#### Paßgenauigkeit von SMD-Komponenten

Regel (Paßgenauigkeit von SMD-Komponenten)

Der maximal zulässige Versatz für die Bestückung von SMD-Komponenten ist ± 100µm für Bauformen ≥ 0402. Der maximale Versatz für Bauformen ≤ 0201 ist ± 50µm.

Bauform 0805 2.00x1.25mm

Lötfläche nach CAD-Vorgabe

Lotpastendepot nach Vorgabe des Baugruppenproduzenten

Bild: Rainer Taube

#### Lotpastendepots und Rückätzung

Die durch die Rückätzung reduzierte Lötfläche führt dazu, daß beim Druck der Lotpaste Lot über die SMD-Fläche hinaus aufgebracht wird. Für einen Abstand ≤ 200µm für Lotpastendepots nimmt das Kurzschlußrisiko zu. Der drc am CAD-System berücksichtig das *nicht*.

Lotpastendepot

SMD-Fläche auf der Leiterplatte

Rückätzung der Lötfläche

Bild: Rainer Taube

#### SMD-Grundflächen versus Schablonen-Innenwand

Für die Auslösung der Lotpaste aus der Schablone sind die Adhesionskräfte auf der Leiterplattenoberfläche (~ SMD-Pad-Geometrie) und der Innenwand der Schablone (~ Schablonendicke + Schablonenöffnung) maßgebend.

Regel (AspectRatio Schablonen-Grundfläche zur Schablonen-Innenwand)

Die Fläche der Schablonen-Innenwand soll nicht größer sein, als das 0.66-fache der Schablonen-Grundfläche.

| Schablonendicke | SMD-Pad    | Grundfläche           |   | Innenwand             |

|-----------------|------------|-----------------------|---|-----------------------|

| 100 μm          | 300x300 µm | 0.071 mm <sup>2</sup> | < | 0.094 mm <sup>2</sup> |

| 100 µm          | 400x400 µm | 0.126 mm <sup>2</sup> | = | 0.126 mm <sup>2</sup> |

| 100 µm          | 500x500 μm | $0.196 \text{ mm}^2$  | > | 0.157 mm <sup>2</sup> |

| 100 µm          | 600x600 µm | $0.283 \text{ mm}^2$  | > | 0.188 mm <sup>2</sup> |

| 150 µm          | 300x300 μm | 0.071 mm <sup>2</sup> | < | 0.141 mm <sup>2</sup> |

| 150 µm          | 400x400 µm | $0.126 \text{ mm}^2$  | < | $0.188 \text{ mm}^2$  |

| 150 µm          | 500x500 μm | $0.196 \text{ mm}^2$  | < | 0.236 mm <sup>2</sup> |

| 150 µm          | 600x600 µm | 0.283 mm <sup>2</sup> | = | 0.283 mm <sup>2</sup> |

#### **Elementare Geometrien: Kugel**

#### Hinweis (Lotkugel)

Lotlegierungen bestehen aus einem pastösen, kugelförmigen Substrat. Allgemein gilt, daß mindestens 5 Lotkugeln nebeneinander in die Schmalseite einer Schablonenöffnung passen sollen. Nimmt die Geometrie eines Bauteilanschlusses ab, dann nimmt auch die Geometrie des Lotpastenpads ab. Die Schablonenöffnung wird schmaler und daher müssen die Lotkugeln im Durchmesser kleiner werden. Mit abnehmen-

Lotpastendruck auf SMD-IC-Pads

dem Kugelvolumen nimmt die reaktive Kugeloberfläche zu und damit die Oxidationsbereitschaft der Lotlegierung.

| Lotkugel Ø | Oberfläche : Volumen |

|------------|----------------------|

| 8 µm       | 750.00 : 1           |

| 11 µm      | 545.45 : 1           |

| 15 µm      | 400.00:1             |

| 38 µm      | 157.89 : 1           |

| 45 µm      | 133.33 : 1           |

| 75 µm      | 80.00 : 1            |

...das war das...

Vielen Dank für Ihr Interesse.

#### Philosophisches zum Ende

Eine einfachere Einfachheit ist nur möglich vor dem Hintergrund einer komplexeren Komplexität.

Gerhard Eigelsreiter, Graz

Komplexe Systeme erzeugen komplexe Fehler.

Berufserfahrung

Alles Gute ist immer einfach. Aber alles Einfache ist nicht immer gut.

Volksmund

Man muß die Dinge so einfach wie möglich machen, aber nicht zu einfach.

Albert Einstein

Quidquid agis, prudenter agas et respice finem.

Äsop

# Informationen zur LeiterplattenAkademie GmbH

#### Die LA - Leiterplatten Akademie GmbH

Die Sicherung des Standortes Deutschland in Europa und der Erhalt der internationalen Wettbewerbsfähigkeit setzt eine systematische und kontinuierliche Qualifikation der Mitarbeiter/innen eines Unternehmens voraus.

Die wirtschaftliche Leistungsfähigkeit einer Industriegesellschaft und ihre technologische Kompetenz am Weltmarkt wird (auch) durch die Qualität ihrer Elektronikprodukte bestimmt.

Das erfordert eine fachlich hochwertige Aus- und Weiterbildung. Wir verstehen es als unserer Aufgabe, Fachwissen in den entscheidenden Bereichen zu vermitteln.

- Schaltplanentwicklung

- CAD-Design

CAM-Bearbeitung

- Leiterplattentechnologie

- Baugruppenproduktion

#### **Ihr Kontakt**

#### **Arnold Wiemers**

Seit 1980 selbstständig als Softwareentwickler für die Kalkulation, die Fertigungsabläufe und Fertigungsleitsteuerung von Leiterplatten.

Ab 1983 angestellter Geschäftsführer für den Fachbereich CAD der ILFA GmbH, Aufbau der CAM in den 1990er Jahren und ab 2000 Technologieberatung für komplexe Leiterplatten.

Seit 2009 Mitinhaber und Technischer Direktor der LA-LeiterplattenAkademie GmbH.

Fachseminare zur Leiterplatten- und Baugruppentechnologie. Mitarbeit am Schulungskonzept der entsprechenden Fachverbände. Vom IPC zertifizierter CID, CID+, CIS 6012, Tutor und Trainer. ZED. Aktives Mitglied im AK-Design des ZVEI.

Förderung der Ausbildung an Berufs-, Fach- und Hochschulen.