|

Seminar und Tutorial Leiterplatten 37

...Impedanzdefinierte Leiterplatten

Analyse und Charakteristik

von Impedanzen auf Leiterplatten

Termine: Leiterplatten 37 wird derzeit ausschließlich in der Kombination "Spezialwissen" angeboten.

|

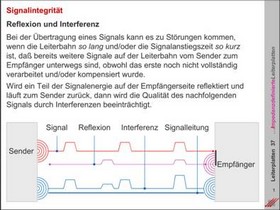

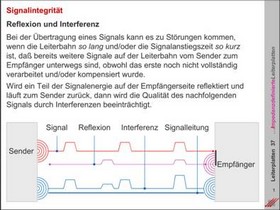

Signalübertragung

Allgemeine Hintergründe zu Highspeed-Leiterplatten und -Baugruppen. Anforderungen an die Signalübertragungsqualität. Reflexion und Interferenzen als Störquelle. Auswirkungen der Signalanstiegszeit (signal rise time) auf das CAD-Design.

|

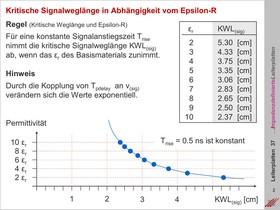

Kritische Weglängen

Auswirkung der kritischen Weglängen auf den Signaltransfer. Abhängigkeit der Weglänge von der Permittivität / dem Dielektrikum des Basismaterials. Kopplung der Signallaufzeit (propagation delay) an das Basismaterial der Leiterplatte.

|

|

|

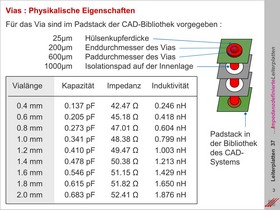

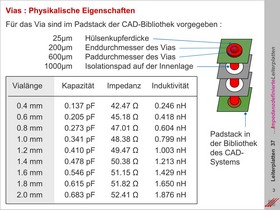

Vias

Physikalische Eigenschaften von Vias für den Lagenwechsel von Leiterbahnen. Berechnung der Kapazität, Impedanz und Induktivität in der realen Umgebung auf Multilayern. Parameterintervalle in Abhängigkeit von der Vialänge.

|

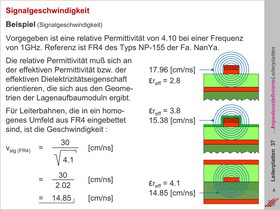

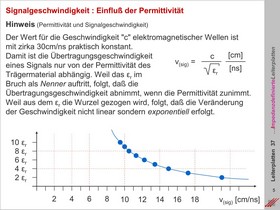

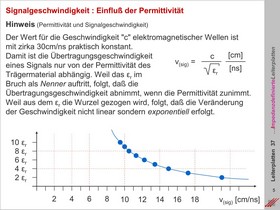

Signalgeschwindigkeit

Einflußsphären um Leiterbahnen. Effektive Signalgeschwindigkeiten in Abhängigkeit von der Positionierung einer Leiterbahn innerhalb eines Multilayer-Systems. Funktionale Beziehungen zwischen der Permittivität des Basismaterials und der Signalübertragung.

|

|

|

Permittivität

Physikalische Eigenschaften des Basismaterials und ihr Zusammenhang zur Übertragungsgeschwindigkeit (propagation delay). Grenzwerte. Signalanstiegszeiten in Abhängigkeit von der eingesetzten Logikfamilie.

|

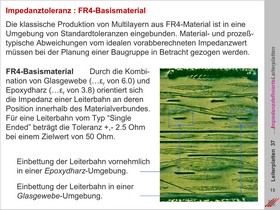

Basismaterial

Diverse Basismaterialien für die Konstruktion von Highspeed Multilayern. Materialklassen auf der Basis von FR4, Keramik, PTFE und Polyimid.

Hersteller und Produkte für Sondermaterialien. Signalgeschwindigkeiten.

|

|

|

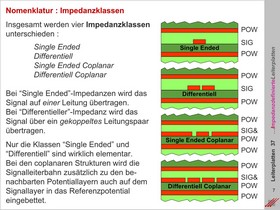

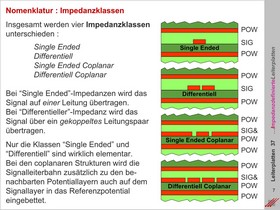

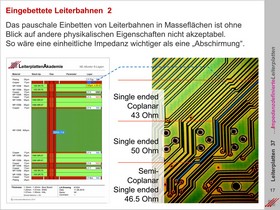

Impedanzklassen

Nomenklatur für die Beschreibung von Impedanzen auf unterschiedlichen geometrischen Moduln. Single Ended, differentielle und coplanare Geometrien. Impedanzen vom Typ Microstrip und Stripline. Erläuterungen zur Kombination von Signal- und Powerplanes.

|

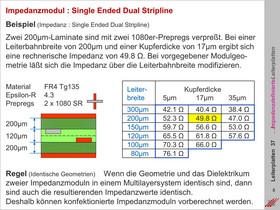

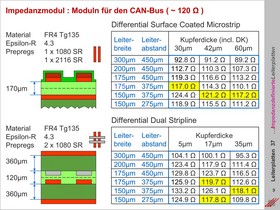

Impedanzmoduln 1

Erklärung der Parameter für die Berechnung von Impedanzmoduln. Vorberechnete Impedanzmoduln für die Konstruktion von Highspeed-Baugruppen. Reale Varianten unter Beachtung der Technologien für die industrielle Fertigung von Leiterplatten.

|

|

|

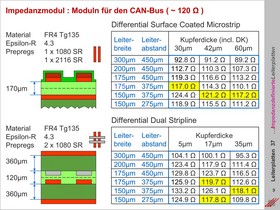

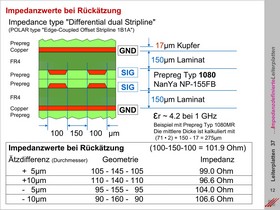

Impedanzmoduln 2

Vorberechnete Impedanzmoduln für die Single Ended und Differentielle Signalübertragung. Beispiele für Dual Stripline sowie coplanare Moduln.Berechnungen für LVDS, FPGA, USB, DDR3 RAM, CAN-Bus und Videosignale.

|

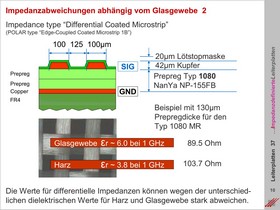

Basismaterial

Grundeigenschaften von Prepregs. Laufzeitverzögerungen durch ungeeignete Glasgewebe bei differentiellem Signaltransfer. Gewebetypen und Prepregvarianten mit unterschiedlicher Harzdicke. Impedanztoleranzen abhängig vom Harzgehalt und vom Preßprozeß.

|

|

|

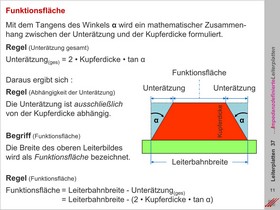

Rückätzung

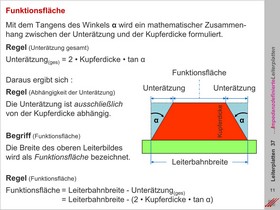

Die Leiterbildstrukturierung als bestimmender Produktionsabschnitt

für die Toleranz eines angestrebten Impedanzwertes. Definition der Rück- und Unterätzung des Leiterbildes über die Formulierung des Ätzwinkels (tangens alpha). Berechnung im Vorfeld einer Multilayerkonstruktion.

|

Fehlerrechnung

Berechnung von Impedanz-Abweichungen in Referenzmoduln. Lötstoplack und Bestückungsdruck als beeinflussende Faktoren. Unregelmäßige Impedanzen in Abhängigkeit von der Ätzmechanik. Querschnittsprofile, Flankenwinkel und Funktionsflächen.

|

|

|

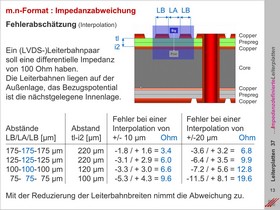

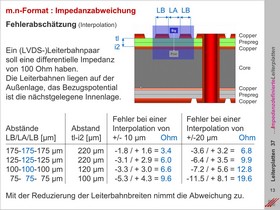

Datenformat

CAD-Postprozeß und Datatransfer. Impedanztoleranzen mit Bezug zur Koordinatenauflösung. Interpolationen wegen eines nicht ideal gewählten m.n.-Formates als Fehlerquelle für eine deutliche Abweichung von der Zielimpedanz.

|

Fertigungstoleranz 1

Basismaterial als vorrangige Einflußgröße auf die Stetigkeit einer Impedanz. Akzeptable und nicht akzeptable Abweichungen mit Referenz zu Geweben und Harzverfüllungen. Toleranzintervalle. Grenzen der Leistungsfähigkeit von FR4.

|

|

|

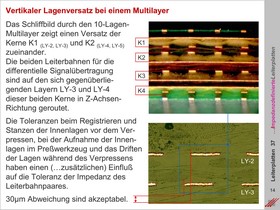

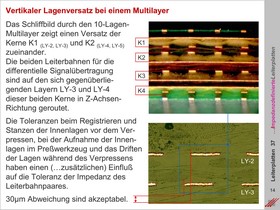

Fertigungstoleranz 2

Fertigungsbedingte Abweichungen. Abweichender Lagenabstand und Registrierversatz durch das Verpressen von Multilayern.

Der Einfluß des Kontaktierens und Ätzens auf den Impedanzwert. Kupferdickenabhängige Blendenkompensation.

|

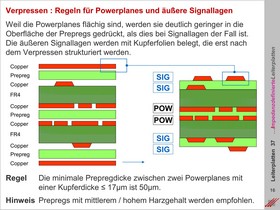

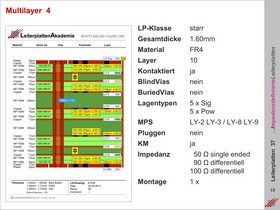

Lagenaufbau

Grundregeln für die Konstruktion impedanzdefinierter Multilayer. Mindestabstände für den Lagenaufbau zwischen Signal- und Powerplanes. Variable Signal-Ground-Abstände durch die unterschiedliche Eindringtiefe des Leiterbildes in das Harz der Prepregs.

|

|

|

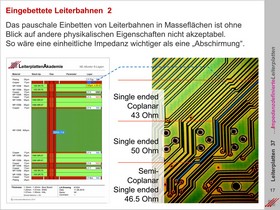

Kritische Impedanzmoduln

Eingebettete Leiterbahnen als Fehlerquelle. Zukünftige Impedanzmoduln mit reduzierten Geometrien für das Leiterbild und mit minimalen Lagenabständen. Falsche und richtige Verteilung der Qualitäten SIG, GND und VCC in einem Multilayer.

|

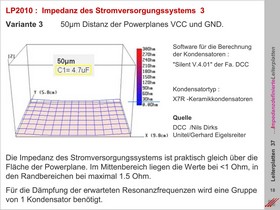

Multipowersysteme

Niederimpedante Konstruktion von Stromversorgungssystemen. Der Einfluß der Abstände zwischen den Powerplanes auf die Funktion des Multilayer-Systems. Gerechnete Kondensatorgruppen zur Dämpfung von Resonanzfrequenzen.

|

|

|

Dokumentation

Dokumentation von Multilayer-Aufbauten als Garant für eine zuverlässige Reproduktion von Leiterplatten in verschiedenen Chargen bei verschiedenen Herstellern.Kennzeichnung von Impedanzen im Lagenaufbau. Filesyntax als kommunikatives Ordnungssystem.

|

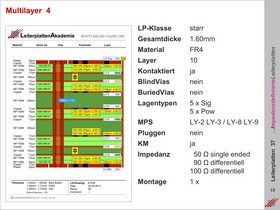

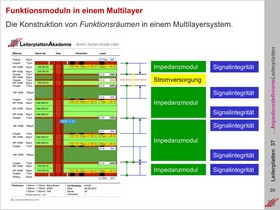

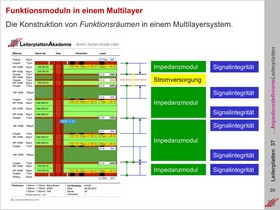

Multilayersysteme

Strategische Aspekte für die Konstruktion impedanzdefinierter Multilayersysteme.

Die Zuordnung von Rückströmen zu Signalintegritätsmoduln. Die Integration von Impedanz- und Stromversorgungsmoduln in die Aufbausystematik eines Multilayers.

|

|

|

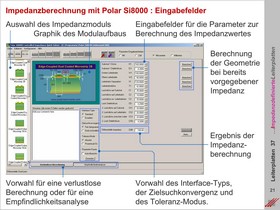

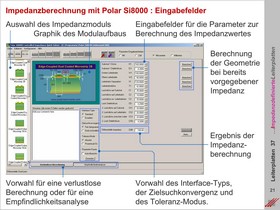

Tutorial (Impedanz)

Übungen zur Impedanzberechnung mit dem Softwareprogramm Si8000 von Polar Instruments. Auswahl geeigneter Geometrien. Parametrisierung der Berechnung. Toleranzberechnungen. Mögliche Fehlerintervalle abschätzen.

|

Wer wird mit dem Seminar und Tutorial "Leiterplatten 37 ...ImpedanzdefinierteLeiterplatten" angesprochen?

Das Halbtagsseminar und Tutorial informiert über die technischen Hintergründe, die zur Forderung impedanzdefinierter Leiterplatten respektive

Multilayern führen. Die Kenntnis der Nomenklatur der elementaren Impe

danzgeometrien sichert die stabile Kommunikation zwischen dem CAD-Konstrukteur und dem Leiterplattenhersteller.

Highspeed-Baugruppen werden ohne die Beachtung der physikalischen

Parameter für die Übertragung von Signalen auf Leiterplatten die Anforderungen an das Leistungsspektrum nicht erfüllen können.

Die Impedanz einer Leiterbahn ist ein zuverlässiger Wert, der von allen

Partnern bewertet, vorausberechnet und nachgeprüft werden kann.

Für die Konstrukteure elektronischer Baugruppen und die CAD-Designer/innen sind die detaillierten Kenntnisse zur Umsetzung von

Impedanzen auf Leiterplatten eine Voraussetzung für die Planung und

Durchführung eines dokumentierten Designs.

"Leiterplatten 37 ...ImpedanzdefinierteLeiterplatten" erläutert die zu

erfüllenden Voraussetzungen für die Planung, Konstruktion und Fertigung von Highspeed-Baugruppen. Referenz und Ziel ist die praktische

Integration impedanzgerechneter Moduln in einen Multilayeraufbau. Die praktischen Beispiele ermöglichen das Erlernen der zu beachtenden

Parameter für die Impedanzberechnung.

Das Tutorial zur Impedanzthematik inklusive der praktischen Berechung üblicher Impedanzmoduln schafft Transparenz und erleichtert das Verständnis für die Anforderungen an die Funktion von Baugruppen.

Das Seminar ist auch für CAM-Bearbeiter/innen der LP-Hersteller von

Bedeutung, weil es die Zusammenhänge zwischen der Funktion einer

Baugruppe und der Fertigung von Leiterplatten erläutert.

Es fördert damit das partnerschaftliche Miteinander auf der Linie "CAD - CAM - Leiterplatte - Baugruppe".

Die Darstellung des Themas ist interessant für alle Entscheidungsträger im Bereich Design und Leiterplatte, deren Aufgabe es ist,

das Produkt "Baugruppe" führend und beratend zu begleiten.

Ihr Referent

|

Arnold Wiemers ist der Leiterplatte seit 1983 verbunden. Von 1985 bis 2009 war er bei der ILFA GmbH in Hannover beschäftigt.

Er war dort verantwortlich für die Fachbereiche CAD und CAM, für die Auftragsvorbereitung und für die technische Dokumentation der Firma ILFA im Internet.

Er arbeitet seit 1982 als freier Softwareentwickler, vornehmlich für branchentypische Applikationen im Bereich der Leiterplatte, wie die Kalkulation und die Fertigungssteuerung von Leiterplatten.

|

Seit 2009 ist er Teilhaber und Technischer Direktor der LeiterplattenAkademie.

Diverse Fachveröffentlichungen. Referent für Seminare, Konferenzvorträge und Workshops zum Thema Leiterplattentechnologie (MFT, MPS, Impedanz, Multilayersysteme, Gerber, Designregeln, LP2010).

Vom IPC zertifizierter CID, CID+ und Instructor. FED-Designer und FED-Referent. Mitarbeit am Schulungskonzept des FED. Mitarbeit in der internationalen "Projektgruppe Design" des FED und des VdL.

Teilnahmegebühren

Leiterplatten 37 wird zur Zeit ausschließlich in der Kombination "Spezialwissen" angeboten.

|